Acqua technical documentation Buy

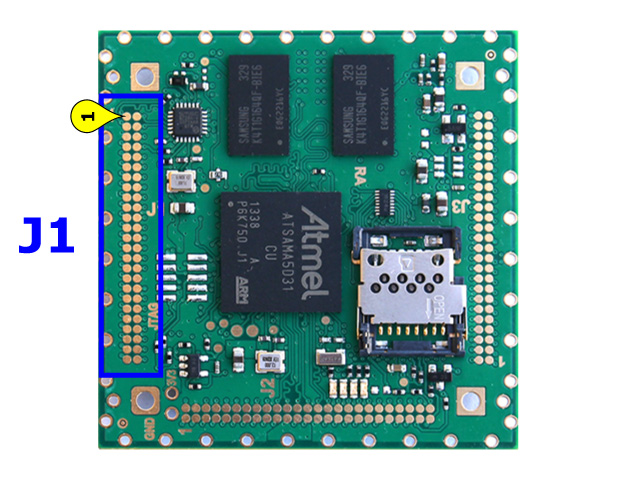

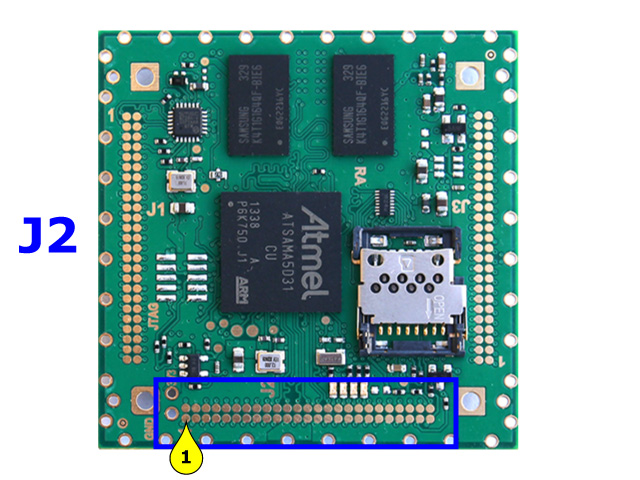

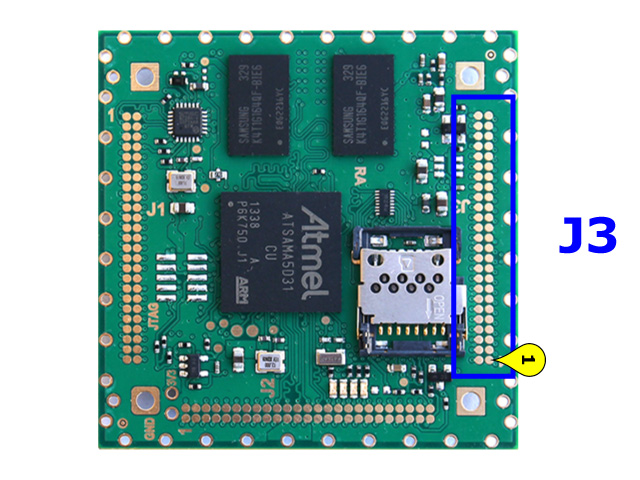

Acqua A5 pinout

- Pin # Acqua A5 pin name

- IC Pin Microchip pin name

- Default Line functions assigned by default by our Linux distribution

- Alt Alternative line functions that can be set changing the device tree binding

- KID Kernel ID using sysfs gpio interface

- Note Any notes about the pin

- Reset state Line state at CPU reset

- PIO indicates whether the PIO Line resets in I/O mode

- A indicates whether the peripheral A mode

- I/O Indicates whether the signal is input or output state.

- PU/PD Indicates whether Pull-Up, Pull-Down or nothing is enabled.

- ST Indicates if Schmitt Trigger is enabled.

The PIO lines called PAx, PBx, PCx, PDx and PEx can be configured in up to four different ways. Please refer to the SAMA5D3 datasheet at page 11 to have a complete reference.

Be carefull to check whether the line reset state is compatible with your application board because it is changed to the Linux default config during the bootstrap after at least 500 ms.

|

|

|

|

- WKUP is a means to wake up the CPU from the shutdown state before the programmed time on a programmable (rise, fall or both ) external event. If not used can be left disconnected.

- SHDN: it is the SHDN pin of the A5 CPU. If instructed to do so, the CPU will lower this signal to disable an external 3.3V power regulator powering the Acqua board. It will work only if you supply a battery backup voltage between 2V and 3V on the VBAT pin. In this way you can shutdown completely the power for the Acqua board (power consumption 0) and wake it up after some time. If not used can be left disconnected.

- POWER_EN: disables some of the internal regulators for factory internal tests. Left it unconnected.

- NRST is a bidirectional external RESET for the CPU. It means you can reset the A5 CPU

from outside but also use the power supervisor inside the Acqua board to reset external chips.

The power supervisor onboard will wait for the power to be stabilized for 140ms before raising the NRST line.

If not used can be left disconnected.

|

|

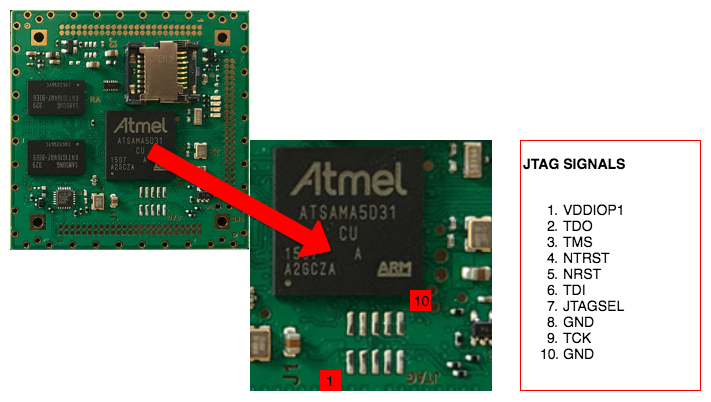

JTag signals

- BOOT_OFF: keeping this line low at startup will disable the boot of the NAND FLASH chip, in order to be able to re-program it with the Microchip tool SAM-BA. If not used can be left disconnected.

- VBAT: if you need the internal RTC working you have to connect a backup battery here, also to enable the timed wakeup as explained above. If not used can be left disconnected.